As electronic miniaturization has been an all-time goal of chip manufacturers, motherboard-based computer/electronic systems have been eventually replaced by System-on-Chip (SoC) and Package-on-Package (PoP) ICs. Complex computer systems are now condensed to smartphones and other handheld devices. These sophisticated electronic devices and gadgets have an SoC at their heart which manages complete computing and control. The SoC package is comprised of several intellectual property (IP) cores. These IP cores come from different chip design companies and vendors.

A scalable, compatible, and efficient data communication between various IP cores in an SoC had been a challenge. This initially was handled by chip designers by laborious redesign, compatibility testing, and designing of additional interfaces. This approach lacked right-first-time coherency leading to costly future re-designs. One of the widely accepted and feasible solutions to this problem was introduced by Arm in 1996 as AMBA protocols.

What is AMBA?

AMBA (Advanced Microcontroller Bus Architecture) is a freely-available, open standard for interconnection and management of IP cores in a System-on-Chip (SoC) IC. It allows right-first-time development of multi-processor chip designs in a modular, reusable, and scalable manner. This helps in avoiding costly re-designs and reduces time-to-market integrated designs.

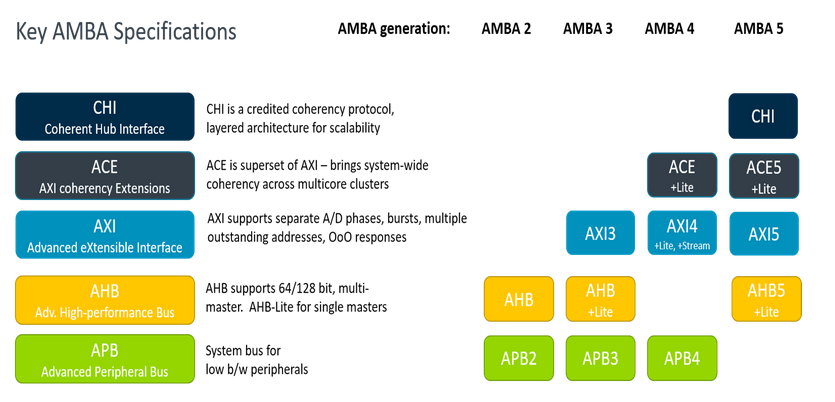

AMBA was first introduced in 1996 with Advanced Peripheral Bus (APB) and Advanced System Bus (ASB) specifications. The second version of AMBA was introduced in 1999 and included Advanced High-Performance Bus (AHB) specifications. AMBA 3 that included Advanced Extensible Interface (AXI), was introduced in 2003. AMBA 4 introduced AXI Coherency Extensions (ACE) in 2010 and AMBA 5, the latest version of AMBA, introduced Coherent Hub Interface (CHI) in 2013.

AMBA Bus system

AMBA Bus system

A traditional AMBA based SoC design uses Advanced System Bus (ASB) or Advanced High-performance Bus (AHB) specifications for high bandwidth communication with blocks like processor, on-chip RAM, memory interfaces, and DMA bus master. While it uses Advanced Peripheral Bus (APB) for low-bandwidth communication with blocks like UART, GPIO, keypad, display, timer, etc, SoCs that have a large number of functional blocks or IP cores require point-to-point interconnect that uses Advanced Extensible Interface (AXI) specifications. The AXI bus manages communication using a master-slave protocol and can be easily bridged with APB. There can be multiple AXI masters and slaves sharing a bus.

Mobile phones and smartphones that contain SoC having multiple processor cores sharing a common cache memory require management of coherency across the memory subsystem. For this, ACE specifications were introduced in AMBA 4. The AXI/ACE specifications were redesigned as CHI to manage communication mechanisms in heterogeneous computing systems. In contrast, to signal based protocol in AXI/ACE specifications, CHI is a packet-based layered protocol that can scale up to communication mechanisms between heterogeneous functional blocks like Digital Signal Processors (DSP), Graphics Processing Units (GPU), I/O subsystems, and memory controllers.

AMBA specifications

AMBA is a set of interconnect protocols. The latest version AMBA 5 includes the following specifications:

- APB: The latest version of the Advanced Peripheral Bus (APB) was introduced in AMBA 2.0. This is a simple non-pipelined protocol that is used for master-slave communication with low bandwidth peripherals. A number of peripherals can be connected to a shared bus, which is managed via a bridge (like AXI-APB bridge) or directly by a master (processor/controller). In APB specifications, the same set of signals are used to read and write over the bus and no burst data transfers are supported.

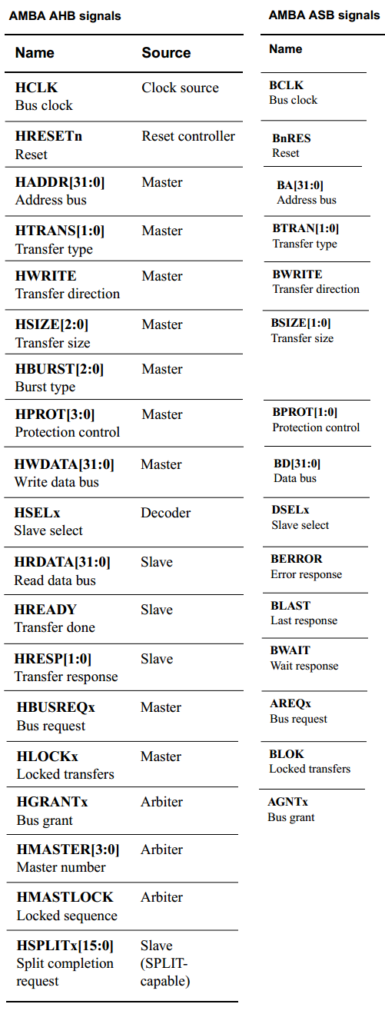

- ASB: The Advanced System Bus (ASB) is a pipelined protocol for communication mechanisms with high-bandwidth and high-frequency components. It supports burst transfers and multiple bus masters. This bus system supports interconnection between multiple masters and memories. The bus consists of four types of blocks – Master, Arbiter, Slave, and Decoder. At any time, only one master can access the bus. A master can only access the bus with the help of an arbiter while it needs selecting a slave for communication using a decoder. The master initiates read or write operation and the selected slave responds to the read and write requests.

- AHB: The Advanced High-Performance Bus (AHB) was introduced in AMBA 2.0. It is an alternative to ASB where high-performance features are required. It supports wider data bus configurations, single-cycle bus-master handover, split transactions, and single clock-edge operations. Like ASB, the AHB bus also requires additional components for managing communication mechanisms like a read multiplexer, write multiplexer, decoder, arbiter, address, and control multiplexer. The bus system consists of three signals – address signal, write data bus, and read data bus. The address signal is used to select a slave, the write data bus is used to move commands from master to the slave, and the read data bus is used to move responses from slaves to masters. The master access the bus by requesting to the arbiter and uses decoder to select a slave. The bus is allotted to a master on the basis of a prioritization scheme. This scheme is defined in the AMBA specifications and differs between different designs. There are 20 different AHB signals in total compared to 15 signals in ASB.

- AHB-lite: It is a simplified version of AHB. It supports communication mechanisms with a single master without the need for any arbiter. It also excludes some high-performance features of AHB like split transactions and retries.

- AXI: The Advanced Extensible Interface (AXI) is a point-to-point interconnect specification that overcomes the limitations of shared bus protocols in connecting multiple agents. It was specifically designed to manage communication mechanisms with multi-core processors and controllers. AXI specifications were introduced in AMBA 3.0. Instead of using a system bus, it uses well-defined interfaces for high-bandwidth and low-latency communication mechanisms. It has several enhanced features compared to AHB, like multiple pipelined transfers, separate read/write wires, wider data bus widths, and burst data transfers.

- AXI-lite: It is a simplified version of the AXI protocol. It lacks burst data transfers compared to full AXI specifications.

- AXI-stream: This is a modification of the AXI protocol for supporting data streaming from masters to slaves. In this protocol, data is moved only in one direction from master to slave. The read/write channels are not separate in AXI-stream unlike in the full AXI specification. It is possible to transfer multiple streams of data between master and slave. This protocol is useful in applications like video streaming, game streaming, etc.

- ACE: The AXI Coherency Extensions (ACE) specifications were introduced in AMBA 4.0. This specification is used to manage communication mechanisms in multi-core processors/controllers with coherent cache memories shared between them. The ACE specification extends the AXI read and write channels using separate snoop address, snoop data channel,s and snoop response channels. These additional channels implement snoop based coherency protocol.

- ACE-lite: ACE-lite is a simplified version of the full ACE specification. It was designed to manage communication mechanisms with agents that do not have a cache memory of their own but still can participate in a sharable coherency system using one-way coherency. Examples of such agents are DMA controllers and Network-on-Chip blocks.

- CHI: The Coherent Hub Interface (CHI) is a redesign of the ACE protocol for much complex heterogeneous computing systems. The ACE protocol uses signal-level master-slave communication interconnecting using a large number of wires and additional channels for snoops and responses. This works fine for small coherent clusters like dual or quad-core mobile SoCs. However, with many heterogeneous components like DSP, GPU, NPU, etc, AXI hits limitations due to being still a signal-based protocol. CHI is a redesign of the AXI bus that uses packet-based interface protocols instead of a signal-based bus system.

Conclusion

If you are in VLSI design, you most likely have heard or learned about AMBA protocols. AMBA has evolved over years to meet the needs of state-of-the-art SoC designs and future IC developments. AMBA protocols are open-standard and can be downloaded from the Arm website after free registration. This article gives you an overview of various AMBA specifications. You can download the specifications from the Arm website and learn about these chip design protocols in more depth.

Filed Under: ARM., Tech Articles, What Is

Questions related to this article?

👉Ask and discuss on EDAboard.com and Electro-Tech-Online.com forums.

Tell Us What You Think!!

You must be logged in to post a comment.