The first working point contact transistor developed by John Bardeen, Walter Brattain and William Shockley at Bell laboratories in 1947 initiated the rapid growth of the information technology industry. In 1958, J Kilby invented the first integrated circuit flip flop at Texas and soon after this; Frank Wanlass at Fairchild described the first CMOS logic gate (nMOS and pMOS) in 1963.

The most common description of the evolution of CMOS technology is known as Moore’s law. In 1963 Gordon Moore predicted that as a result of continuous miniaturization, transistor count would double every 18 months. The observation made by Gordon Moore was that the number of components on the most complex integrated circuit chip would double each year for the next 10 years. This doubling was based on a 50 – 60-component chip produced at that point of time compared with those produced in preceding years. Looks surprising, but his prediction has turned true and is being treated as a law. The speed of transistors increases and their cost decreases as their size is reduced. The transistors manufactured today are 20 times faster and occupy less than 1% of the area of those built 20-30 years ago. In 1971, Intel 4004 had transistors with minimum dimension of 10um and in 2003; Pentium 4 had transistors with minimum dimension of 130 nm. Having crossed 90nm, 65nm technological nodes, 32 nm and 22nm technology is in the pipeline. 53% compound annual growth rate is achieved over 45 years. No other technology has grown so fast so long. Transistors have become smaller, faster, consume less power, and are cheaper to manufacture. It seems intuitively obvious that scaling cannot go on forever because transistors cannot be smaller than atoms.

The first integrated circuits hitting the markets in the seventies had a few 100 transistors integrated in bipolar technology. Even though the principles were well known, MOS arrived in the markets several years later. One of the reasons behind this was the inherent instability of the MOS transistors due to the presence of minute amounts of alkali elements in the gate dielectric. This caused the threshold voltage of the transistor to shift during the operation.

However, soon the problems of high power consumption by bipolar circuits became dominant. Even in the case of all transistors being ‘OFF’, the sum of the leakage current in bipolar transistors is fairly large. To provide a solution for the problem of power consumption, MOS technology eventually made its way. Dimensions of MOS devices can be scaled down more easily than other transistor types.

In principle, MOS is better in terms of power consumption. MOS devices work with only switching voltages; current per se is not needed for the operation. MOS circuits do have lower power consumption; but they are also slower than their bipolar colleagues. Initially, NMOS got wider acceptance but with the increase in integration density, power consumption again became a problem. Afterwards, in eighties, CMOS processes were widely adopted. Present day chips would not exist if the CMOS technique would not have been implemented around the late eighties.

IC TECHNOLOGIES

Silicon IC technologies can be primarily classified under three types:

{C· Bipolar

Bipolar transistors have npn or pnp silicon structure. In these transistors, small current into very thin base layer controls large currents between emitter and collector. Base currents limit integration density of bipolar devices.

{C}· Metal Oxide Semiconductor(MOS)

MOS is further classified under PMOS (P-type MOS), NMOS (N-type MOS) and CMOS (Complementary MOS). MOS derives its name from the basic physical structure of these devices; MOS devices comprise of a semiconductor, oxide and a metal gate. Nowadays, polySi is more widely used as gate. Voltage applied to the gate controls the current between source and drain. Since they consume very low power, MOS allows very high integration.

{C· BiCMOS(Bipolar CMOS technology)

BiCMOS Technology utilizes both CMOS and Bipolar Junction transistors integrated on the same semiconductor chip.

CMOS offers high, symmetrical noise margins, high input and low output impedance, high packing density, and low power dissipation but speed is the only restricting factor. In contrast, the ECL gate has a high current drive per unit area, high switching speed, smaller propagation delay, but high power consumption makes very large scale integration difficult.

BiCMOS has made it possible to combine CMOS transistors and bipolar devices in a single process at a reasonable cost to achieve the high-density integration of MOS logic with the current-driving capabilities of bipolar transistors.

Some other variants of FETs have also come up, viz., Si-TFT, polySi-TFT, MESFET, etc. These are used for different applications.

PMOS and NMOS: CMOS Basics

CMOS BASICS

Before exploring CMOS let’s look into NMOS and PMOS.

{C}{· NMOS

The first letter ‘N’ refers to the kind of carrier that carries current flow between source and drain as soon as the threshold voltage is crossed. Thus, NMOS stands for transistors where negatively charged carriers, i.e., electrons are the current carriers between source and drain.

Physical structure of NMOS device is shown below

Fig. 1: A Diagram Representing Physical Structure of NMOS Device

[[wysiwyg_imageupload:NMOS:]]

Operation of the device is listed below

¨ Body is commonly tied to ground (0 V)

¨ When the gate is at a low voltage:

¨ P-type body is at low voltage

¨ Source-body and drain-body diodes are OFF

¨ No current flows, transistor is OFF

¨ When the gate is at a high voltage:

¨ Positive charge on gate of MOS capacitor

¨ Negative charge attracted to body

¨ Channel under gate gets “inverted” to n-type

¨ Now current can flow through n-type silicon from source through channel to drain, transistor is ON

NMOS operation is depicted pictorially in the following figure.

Fig. 2: A Diagram Illustrating Operation of NMOS

Fig. 3: A Diagram Illustrating Multiple Operation of NMOS

Cons of NMOS

· Output Low consumes power

· Pull-up “weaker” than pull-down

· Need resistors

Pros of NMOS

· For X inputs: X NMOS Transistors

{C}{· PMOS

PMOS stands for transistors where positively charged carriers flow, i.e. holes are the current carriers. This implies that source and drain must be p-doped areas in an n-doped substrate; the current flow begins as soon as inversion sets in, i.e. the n-type Si between source and drain is inverted to Si with holes as the majority carriers.

Physical structure of PMOS device is shown below

Fig. 4: A Figure Representing Physical Structure of PMOS

Operation of PMOS device is similar to that of NMOS but doping and voltages reversed

¨ Body tied to high voltage (VDD)

¨ When Gate is low: transistor is ON

¨ When gate is high: transistor is OFF

¨ Bubble indicates inverted behavior

VGS > VTN

VGS > VTN

VGS <= VTN, VDS<= VDSAT

CMOS & its Fabrication

{C}{· CMOS

CMOS has characteristics very close to that of an ideal logic family. Ideal logic family should dissipate no power, should have zero propagation delay, controlled rise and fall times, and have good noise immunity.

NMOS and PMOS transistors are not ideal switches. NMOS pass strong ‘0’ but a degraded or weak ‘1’ (pull no higher than VDD-Vtn); whereas PMOS pass strong ‘1’ but a degraded or weak ‘0’ (pull no lower than |Vtp|). Hence, NMOS are best for pull-down network, whereas PMOS are best for pull-up network.

CMOS takes the merits of both, NMOS and PMOS. CMOS technology uses NMOS and PMOS transistors. The transistors are arranged in a structure formed by two complementary networks, viz. Pull Up Network and Pull Down Network (PDN). Since there is no static current flow; only a small amount of dynamic current exists while switching takes place, CMOS device consume very small amount of power.

PUN: Pull Up Network

PDN: Pull Down Network

|

|

Pull Up OFF |

Pull Up ON |

|

Pull Down OFF |

Z(float) |

1 |

|

Pull Down ON |

0 |

X(Crowbar) |

CMOS gates always produce ‘0’ or ‘1’. Depending on the right polarities, the PMOS transistor will be closed if there is a gate voltage – the output then is zero. For gate voltage zero, the NMOS transistor will be closed, the PMOS transistor is open – the output will be VDD

Pros of CMOS

· No static power consumption

· Pull-up symmetric with pull-down. Output swings to full range

· Both high to low and low-to-high transitions are fast because of low resistance of pull-up transistors unlike the load resistors in NMOS logic

Cons of CMOS

· For X inputs: 2X CMOS Transistors are needed.

CMOS FABRICATION

Complexity and the cost of fabrication are governed by the number of masks fabrication technology uses. CMOS process requires seven masks, & 34 process steps. Minimum dimensions of masks determine transistor size (and hence speed, cost, and power)

Technology nodes are defined by the feature size; Feature size f = distance between source and drain is set by minimum width of polysilicon. While describing design rules, feature size is normalized. Design rules are expressed in terms of l = f/2, e.g. l = 0.3 mm in 0.6 mm process

Major fabrication steps for a CMOS process are as follows:

a) Growth of SiO2 on p-type wafer

b) Creation of p and n wells

CMOS technology requires fabrication of two different transistors- NMOS and PMOS on a single chip substrate. Actually, NMOS and PMOS needs substrates with different kind of doping in one integrated circuit but such substrates do not exist; a Silicon wafer always has one doping type and doping level. Hence, to accommodate both NMOS and PMOS transistors, CMOS technology requires creation of special regions by impurity implantation in the substrate; semiconductor type in these regions is opposite to the base substrate type. These regions are called wells or tubs. A p-well is created in an n-type substrate or, alternatively, an n- well is created in a p-type substrate. Thus, if base substrate is p-type, NMOS transistor is created in the p-type substrate while PMOS transistor is created in the n-well built in the p-type base substrate.

It involves three steps

(a) Photolithography to define n-well area

(b) Ion Implantation to create n-well

(c) Removal of PR and oxide layer.

c) Channel Stop Implant

It is required to prevent conduction between unrelated transistor sources and drains.

Region between two n+ regions is covered with field oxide and metallization on top of it. This forms a transistor, though with large threshold, and introduces parasitics.

Channel stop implantations are done with the help of 5 process steps.

(a) Create a stack of Silicon Oxide, Silicon Nitride and positive photoresist layers.

(b) Photolithography to define channel implant areas

(c) Channel Stop Ion Implantation

(d) Removal of PR. Growth of thick oxide layer in areas where Silicon Nitride is not there.

(e) Removal of Thin Silicon Oxide, Silicon Nitride layers.

CMOS Fabrication contd.

d) Growth of Gate Oxide to serve as gate dielectric

Thickness of gate dielectric affects number of parameters of MOSFETs, viz., current handling, transconductance, reliability. Uniform thickness of this layer is pretty important.

e) Threshold adjust implant

Native threshold value typically is far from the desired values (VTHN~ 0V and VTHP~ -1 V). Hence thin layer of dopants are implanted to adjust it.

f) Create PolySi Layer

It involves two steps

(a) Deposit PolySi on top of Gate Oxide

(b) Photolithography to remove SiO2 using ‘PolySi’ mask

g) N-type Implant

It involves three process steps

(a) Photolithography using ‘N Drain/Source mask’

(b) Ion implantation to form Source & Drain regions

(c) Removal of PR

h) P-type Implant

In similar fashion, p+ regions are created

i) Silicidation

Silicidation is done to reduce sheet resistance of doped PolySi and source/drain regions. This process involves deposition of thin layer of highly conductive material (titanium silicide and tungsten). It involves two process steps

(a) Creation of oxide spacers at edges of PolySi gate.

(b) Deposition of conductive material through CVD process.

j) Contact Windows

It involves following steps

a) Cover wafer with a thick layer of oxide

b) Photolithography using contact mask

c) Plasma etching

k) Metal Interconnect

It involves following steps

a) Deposit a layer of metal

b) Photolithography using Metal Mask

l) Via Windows

It involves following steps

a) Deposit a layer of SiN3

b) Photolithography using Via Mask

m) Metallization

a) Passivation & Bond Pads

Wafer is covered with a layer of glass to protect the surface against the damages. Finally bond pads are created.

CMOS v/s BJT and CMOS Logic

COMPARISION OF THE FEATURES OF CMOS & BJT DEVICES

· Compared to BJT CMOS devices are low power consumption device. Power is drawn only during switching of states in CMOS.

· CMOS is uni-polar but BJT is bipolar.

· Manufacturing is easier for CMOS rather than BJT.

· CMOS is voltage controlled device, BJT is current controlled device.

· CMOS has very high input impedance; BJT is having relatively low input impedance. Hence, CMOS devices will have less loading effect

· CMOS is more sensitive to electrostatic discharge compared to BJT.

· MOSFET has higher immunity towards radiation compared to BJT

· BJT is very high speed switching device and hence can be used at higher frequencies compared to CMOS

· CMOS have high noise margin rather than BJT.

· Integration density is better in CMOS

· CMOS produce less amount of heat

CMOS LOGIC

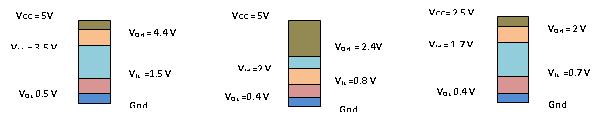

Different logic families use different voltage levels for logic ‘high’ and logic ‘low’. For 5V CMOS family, voltage levels are VIL = 1.5 V, VOL = 0.5 V, VIH = 3.5 V, VOH = 4.4 V & for 2.5 V CMOS family, voltage levels are VIL = 1.5 V, VOL = 0.5 V, VIH = 3.5 V, VOH = 4.4 V. In 5V TTL logic family voltage levels for logic ‘high’ and logic ‘low’ are VIL = 0.8 V, VOL = 0.4 V, VIH = 2 V, VOH = 2.4 V. Similarly, voltage levels are different for ETL, TTL/CMOS, etc logic devices.

5V CMOS 5V TTL 2.5 V CMOS

The CMOS have different input and output switching levels than the TTL logic devices. The output switching levels from CMOS ICs is higher than a TTL IC, which happens to result in a better design and does not have a negative effect. However the difference in input logic switching level does affect the design. The TTL output does not correctly switch a CMOS input. The switching difference between a TTL IC output and a CMOS IC input has to be accounted for. In CMOS the floating input is interpreted as an uncertain and In TTL the floating input is interpreted as a logical low.

Also, TTL (Transistor-Transistor Logic) need a narrow range of supply voltage (around 5V) but CMOS (metal oxide semiconductor field effect transistor) devices have a wider voltage range between 3-12 V.

BASIC CMOS CIRCUITS

{C1. Inverter

|

A |

Y |

|

0 |

1 |

|

1 |

1 |

NAND Gate

|

A |

B |

Y |

|

0 |

0 |

1 |

|

0 |

1 |

1 |

|

1 |

0 |

1 |

|

1 |

1 |

0 |

NOR GATE

|

A |

B |

Y |

|

0 |

0 |

1 |

|

0 |

1 |

0 |

|

1 |

0 |

0 |

|

1 |

1 |

0 |

Filed Under: Articles

Questions related to this article?

👉Ask and discuss on EDAboard.com and Electro-Tech-Online.com forums.

Tell Us What You Think!!

You must be logged in to post a comment.