SR flip-flop is a short form of set-reset flip-flop. Its output is either set means high (logic 1) or reset means low (logic 0) as per set or reset inputs given. When set input is given logic 1 (high), the flip-flop is set and its Q output is high (another complemented output QBAR will be low) and when reset input is given logic 1, the flip-flop is reset and its Q output is low (QBAR output will be high). In clocked SR flip-flop, the output states will change only when a clock pulse is applied along with S & R inputs.

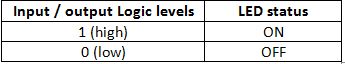

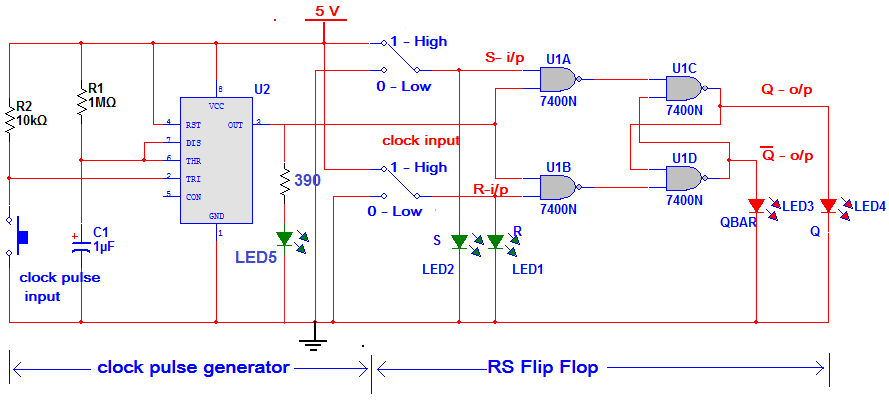

Here, the given circuit demonstrates the operation of clocked SR flip-flop. The flip-flop is built using four 2 input NAND gates and clock pulse generator is built using multivibrator chip IC NE555. SPDT switches are used to give S and R inputs as logic 1 (high – 5 V) and logic 0 (low – 0 V). Different RED and GREEN LEDs are used for input-output logic indications. Please refer the table given below.

Fig. 1: Table listing LED Status for Logic Levels of 555 IC based Clocked SR Flip Flop

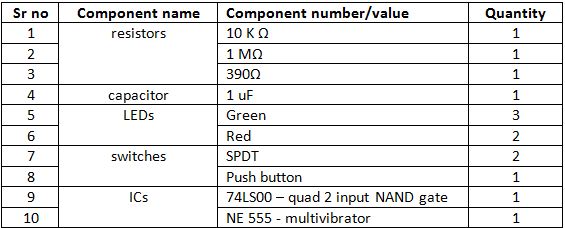

The circuit is very easy to build and all the components are also easily available and cheap. Here is the list of required components.

Fig. 2: List of Components required for 555 IC based Clocked SR Flip Flop

The circuit can be built on general purpose PCB or breadboard. So let us see the circuit diagram followed by its description and operation.

CIRCUIT DESCRIPTION

The complete circuit is divided into two different sections -:

2. RS flip flop circuit

Clock pulse generator circuit is built using IC NE555. IC NE555 is wired in monostable mode. Timing components R1 and C1 are chosen such as to give pulse output of 1 sec approx. A push button is connected to trigger input pin 2. The output of IC is given as clock pulse input to the flip-flop circuit. One LED is connected (LED5) to this output to indicate clock pulse output from the circuit.

SR flip-flop circuit is built using quad 2 input NAND gate chip 74LS00. The circuit consists of 4 2 input NAND gates, 2 SPDT switches for input and 4 LEDs for indications and outputs. Two SPDT switches provide logic 1 (high) or logic 0 (low) to S and R inputs. The status of S and R inputs is indicated by two green LEDs LED1 and LED2. The Q and QBAR outputs of the flip-flop are connected to two red LEDs LED3 and LED4 as shown. The complete circuit works on 5 V supply.

Here is the snap of circuit arrangement.

Fig. 3: Prototype of 555 IC based Clocked SR Flip Flop

CIRCUIT OPERATION

Clock pulse generation circuit – because IC NE555 is wired in a monostable mode it will generate 1 sec pulse every time when a trigger input is applied by pressing push button. The LED blinks to indicate clock pulse is generated.

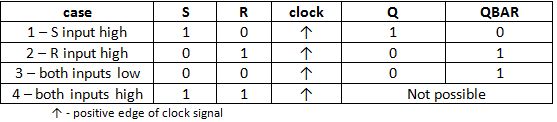

SR flip-flop circuit – The circuit works as per following truth table.

Fig. 4: Truth Table of Clocked SR Flip Flop

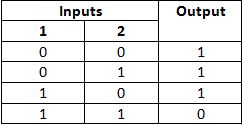

First, S is given logic 1 input and R is given logic 0 input through SPDT switches. Now when the clock pulse is given from clock pulse generator circuit, the two inputs of U1A gate become high (logic 1). So as per NAND gate operation* its output goes low (logic 0). As this output is connected to one input of U1C, the output of U1C becomes high immediately as per NAND gate truth table*. The Q output is high and LED4 glows. This output is given as input to U1D. Another input to U1D is from U1B and that is also high because its input R is low. So now, as both the inputs of U1D are high, its output will go low. Thus QBAR output is low and LED3 is off.

In the second case, S input is given logic 0 and R is given logic 1. When clock input is high, the two inputs of U1B gate become high (logic 1). So its output goes low (logic 0). As this output is connected to one input of U1D, the output of U1D becomes high immediately. The QBAR output is high and LED3 glows. This output is given as input to U1C. Another input to U1C is from U1A and that is also high because its input S is low. So now, as both the inputs of U1C are high, its output will go low. Thus Q output is low and LED4 is off.

Similarly in 3rd case, when both S and R inputs are low, the Q and QBAR outputs will remain as it was previously. There will be no change in Q and QBAR output.As given in the last case, we cannot apply both S and R inputs as high. This will make the outputs of gates U1A and U1B low and this would make outputs of U1C and U1D high. That means Q and QBAR both outputs will be high. And this must not happen. That’s why we cannot apply both S and R inputs high.

*NAND gate truth table

Fig. 5: Truth Table of NAND Gate

Circuit Diagrams

Project Video

Filed Under: Electronic Projects

Filed Under: Electronic Projects

Questions related to this article?

👉Ask and discuss on EDAboard.com and Electro-Tech-Online.com forums.

Tell Us What You Think!!

You must be logged in to post a comment.