Renesas Electronics Corporation recently announced that it has come up with an AI accelerator that does Convolutional Neural Network (CNN) processing at low power consumption and high speeds. This development marks a crucial step towards coming range of embedded AI by the premier supplier of advanced semiconductor solutions. This new solution will accelerate enhanced intelligence of endpoint devices.

The new chip features a power efficiency of 8.8 TOPS/W that classifies as the highest power efficiency class in the industry. This new accelerator takes root into Processing-in-memory (PIM) framework. PIM is one of the most preferred approaches towards AI technology. It includes multiply-and-accumulate operations taking place inside memory circuit as data gets read out from memory.

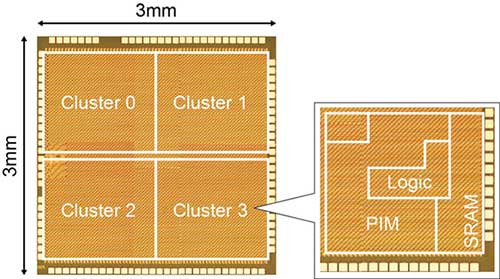

Fig. 1: Image Showing The Next-Gen AI Chips Developed By Renesas

Renesas developed three technologies to create this new AI accelerator:

- Ternary-Valued SRAM Structure PIM Technology: It is capable of performing some of the most huge-scale CNN computations.

- SRAM Circuit: This one is implemented with comparators that read out memory data when power levels are too low.

- The last one keeps calculation errors at bay for processing variations during manufacturing.

Altogether, these three technologies are capable of reaching reduction in memory access time for the deep learning process as well as these bring down the power needed for multiply-and-accumulate operations. Therefore, the new accelerator can reach the highest class of industry’s power efficiency while keeping up the precision ratio above 99%.

Till date, the PIM architecture wasn’t capable of achieving a sufficient precision level for larger scale CNN computations with single-bit calculations because the binary SRAM structure can handle data with values 0 or 1. Also, the process variations in manufacturing lead to reduction in reliability of such calculation and called out for more rectifications. The new technologies developed by Renesas to resolve such issues and will be implementing these in all future AI chips.

Key Features

- Ternary (1,0,-1) SRAM structure PIM capable of adjusting its calculation bit as per the needed precision.

- Low-power/high-precision memory data readout circuit that includes replica and comparators cells.

- Variation avoidance technology keeps doan the calculation errors in manufacturing.

Filed Under: News

Questions related to this article?

👉Ask and discuss on Electro-Tech-Online.com and EDAboard.com forums.

Tell Us What You Think!!

You must be logged in to post a comment.