What is Decimal Counter?Decimal counter is same like a stop watch. Take example of a counter from 0 up to 100. In decimal counter same like stop watch the unit place starts from 0 and goes up to 9. When unit place reaches 9 it increments the tenth place by 1 and resets it self. Again the unit place starts from 0 and counts up to 9, resets it self and increments the tenth place. When tenth place reaches 9 it resets it self now while increments the hundredth place

|

Decimal counter in vhdl

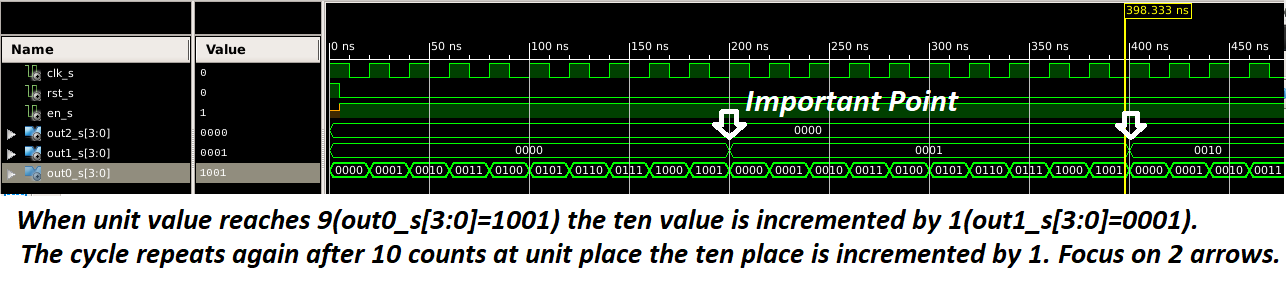

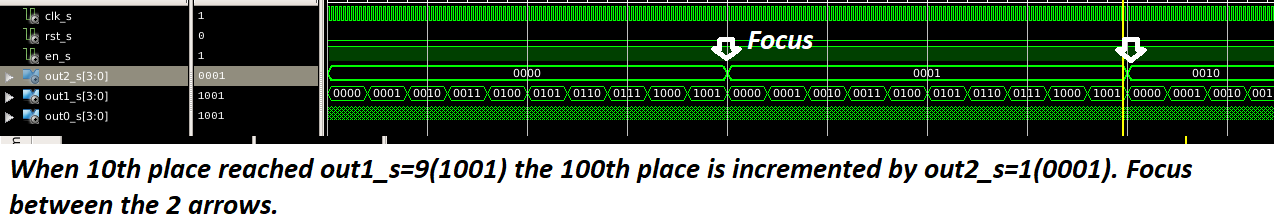

In the below simulation figure out0_s[3:0] is unit place port and out1_s[3:0] is tenth place port. Focus on the arrow points. When out0_s[3:0] unit place reaches 9(1001 is hexadecimal representation of whole number 9). The out1_s[3:0] tenth place is incremented by 1 and out0_s[3:0] is reset to 0.

In entity their are three input ports. Reset port resets the decimal counter to 0. Enable port enables the decimal counter and at last the clock is input to the digital system. Which means that the system works on clock. The three outputs out0, out1 and out2 are decimal counter outputs. They represent unit place out0, tenth place out1 and hundredth place out2. The outputs are 4-bit wide because the max they count is 9 whose binary is 1001.

In the architecture first few signals are defined. These signals are used in replacement of the output ports to count values internally and increment them. Internal signals are assigned to the output ports after necessary computation.

In the process block on reset all the internal signals are assigned 0. Note that the system is asynchronous. Which means reset does not depend on any state(rising/falling edge) of clock. But if reset in not active the control jumps to else state in which it is checked that if enable is activated? If enable is found activated then on the next rising edge of the clock the internal signals are assigned to the output ports. So every new output appears at output ports on rising edge of clock provided the enable is activated.

After the process block the conditions on unit, tenth and hundredth digits are checked, calculated and assigned to internal signals. These signals at the end are assigned to the output ports. The use of FSM(finite state machine) is visible in the code. This tutorial only deals with the code flow. I supposed that you are familiar with the current and next state finite state machine.

Decimal counter test bench

The second process first resets the decimal counter. Reset is important. It assigns our internal signals initial value which is 000. Then after first rising edge of clock it deactivates the reset port and activates the enable port. After enable is activated i used a for loop to count to 1000 rising edges of clock. In the process of 1000 rising edges our decimal counter also reaches 999. After it i disabled the enable port.

Filed Under: Microcontroller Projects, VHDL

Questions related to this article?

👉Ask and discuss on EDAboard.com and Electro-Tech-Online.com forums.

Tell Us What You Think!!

You must be logged in to post a comment.