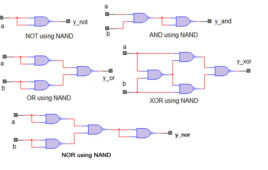

In previous tutorials VHDL tutorial (#6), we built a circuit for D Morgan’s Theorems in VHDL and verified its output to prove D Morgan’s theorems. (If you are not following this VHDL tutorial series one by one, you are requested to go through all previous tutorials of these series before going ahead in this tutorial)…

Decimal counter designed in vhdl

This tutorial is about designing a decimal counter in vhdl. I used xilinx to write code and for simulation i used Isim simulator. The decimal counter i designed starts from 0 and moves up to 999. Counter is working perfectly in simulation. What is Decimal Counter? Decimal counter is same like a stop…

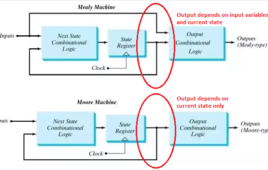

Melay machine finite state machine design in vhdl

This tutorial is about implementing a finite state machine is vhdl. I will go through each and every step of designing a finite state machine and simulating it. Xilinx is used as a tool to construct finite state machine and for simulation and testing purpose. I suppose you know what is finite state machine and…

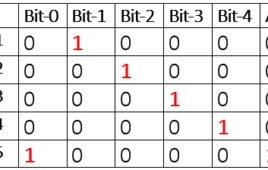

N-bit Ring Counter made using VHDL

A ring counter as the name depicts is a closed loop. Normally in counters their is an increment or decrement in the output depending on if its a up or down counter. In contrast to up and down, ring is some what a fixed counter. Only a specified number of bits revolve around in a…

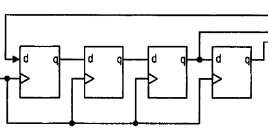

Linear-feedback shift register (LFSR) design in vhdl

LFSR stands for linear feedback shift register. Although they are widely used in random electronics projects but they are quiet often neglected by the engineers community. LFSR is comprised of a series of D-flip flops, depending on the size of the LFSR. Some of the states and especially the last one is feed back to the…

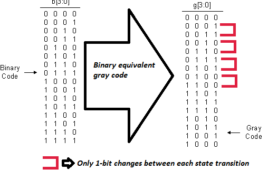

N-bit gray counter using vhdl

This tutorial is about designing an N-bit gray counter in vhdl. I am using xilinx software tool to design and test the gray counter. So what is gray counter? A gray counter changes 1-bit only during one state to another state transition. The counter is same like the normal incremental counter. The only difference is…